# Low Noise L band PLL-VCO designed for the IRNSS -Rx using BiCMOS 180 nm Process

Pankaj S Bhavsar<sup>1</sup>, Shalabh Gupta<sup>2</sup>, Jolly dhar<sup>1</sup>, Ch. V. N Rao<sup>1</sup>, Tapan Misra<sup>1</sup>

<sup>1</sup>Space Applications Centre (SAC), Indian Space Resarch Organization (ISRO), Ahmedabad Microwave sensors Receiver Division (MSRD&AD), Microwave Remote Sensing Area (MRSA)

<sup>2</sup>Department of Electrical Engineering, Indian Institute of Technology Bombay, Powai, Mumbai – 400076.

pankajjain@sac.isro.gov.in

Abstract --- A Low Noise L band PLL-VCO designed for the IRNSS-Rx using Sbc18h2 180 nm BiCMOS SiGe 180 nm Process.

A SiGe HBT (heterojunction bipolar transistor) BiCMOS process have been used for the very low noise VCO design. NPN transistors based cross coupled architecture have been used for the low noise VCO design. Complete PLL integration with VCO have been designed and tested. Very good phase noise has been achieved from the BiCMOS based VCO. PLL is successfully locked and working. The designed BiCMOS PLL is not only giving the better phase noise performance but also better spurious rejection in the locked condition have been achieved.

#### 1. INTRODUCTION

Voltage controlled oscillator are an integral part of many high frequency analog and clock signal generation systems. These VCO designed generally embedded in a phase-locked system. RF subsystems always demands for the low phase noise VCO. A SiGe HBT (heterojunction bipolar transistor) BiCMOS process have been used for the design of the very low noise VCO.

# 2. DESIGN DESCRIPTION

For this SBC18h2 180 nm SiGe process have been used which has the Ft of around 200 GHz. The used HBT process modules are designed to offer a significant performance gain for this one device as compared with other existing SiGe BiCMOS technologies. Very low noise PLL using VCO designed in the 180 nm SiGe BiCMOS Process have been designed.

For the integration of the PLL modules vz. PFD, Charge pump, prescalar various buffers have been designed.

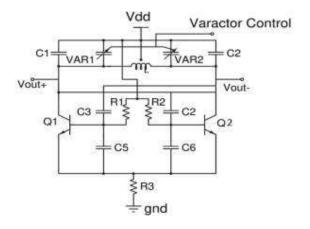

Fig.1 Schematic of the Low Noise VCO designed using HBT based NPN Transistors

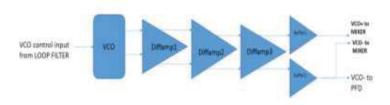

Fig.2 Block diagram of HBT based differential VCO

#### 3. DESIGN METHODOLOGY

# 3.1 VCO:

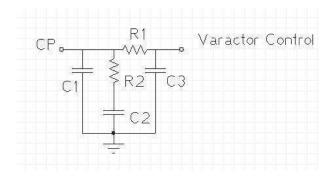

By utilizing the HBT process low phase noise VCO have been designed. A cross coupled NPN transistor pair Q1 & Q2 is used for the negative - Gm implementation. For the Frequency tunning MOS transistor based varactor bank VAR1 and VAR2 have been implemented. MOS varactors provides better supply noise rejection and also less affected by the tank voltage. Use of high Q Differential Inductor L not only make the layout more compact, but also improves the phase noise performance of the VCO. The MIM capacitors C3 and C2 reduces the effect of Cbc by providing

negative miller capacitance. The MIM capacitors C5 and C6 enhance the negative resistance and improves the phase noise performance. C1 and C2 are fixed MIM type capacitors calculated as per the are required L-band free running frequency of the VCO. HBT based differential Cascode amplifier in the second stage of the VCO has been implemented before interfacing the VCO with the based differential amplifiers. equivalent resistance of the cross coupled pair is -2/gm and hence, it will be necessary that  $Rp \ge -$ 1/gm, so that the circuit can behaves as a feedback system with the negative resistance in parallel with the lossy tank. This VCO is called as the negative Gm Oscillator. The fully integrated VCO occupies an active area of 0.6 mm x 1mm.

# 3.2 PLL:

VCO has been integrated with the respective PLL blocks PFD, charge pump, prescalars, Loop filter with the division factor of the 72. PLL is the 2 order type has been designed in order to lock the reference frequency of the 16.36 MHz. Multiples analog and digital buffers have been added to achieve the integrated performance. Designed PLL is 2<sup>nd</sup> Order System with passive external loop filter.

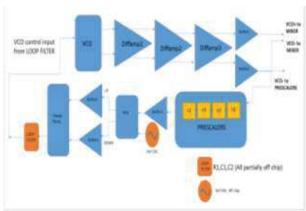

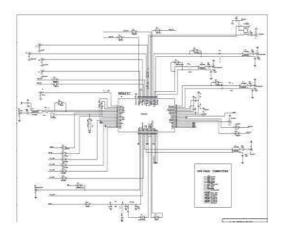

Integration of the PLL has been done as per the Fig shown below.

Fig.3 Integrated PLL block diagram

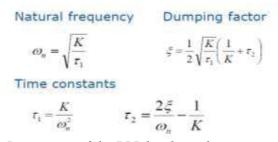

Loop Filter off chip components are calculated *keeping the keeping the phase margin* > 45°

Fig 4. 2<sup>nd</sup> order Loop filter

# 4 RESULTS AND DISCUSSIONS

#### 4.1 VCO:

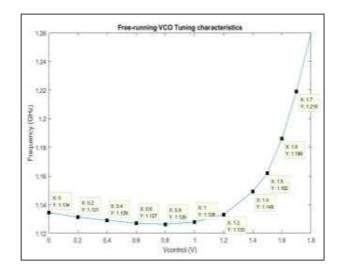

It has been designed with the Cross coupled LC tank based architecture. Successive HBT and CMOS based buffers have been used for the Reverse isolation and Gain. HBT based VCO has been implemented in order to achieve good phase noise performance. VCO has a tuning range from  $1.13 \, \text{GHz} 1.23 \, \text{GHz}$ . KVCO is  $2\pi^* 100 \, \text{MHz} / 0.6$  volt. Phase noise is  $137 \, \text{dBc/Hz}$  at the  $10 \, \text{MHz}$  offset.

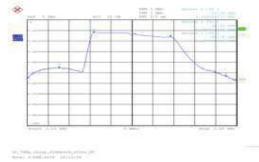

Fig.5 VCO test results Control Frequency Vs Voltage

# PLL:

VCO has been integrated with the respective PLL blocks PFD, charge pump, prescalars, Loop filter

with the division factor of the 72.PLL is the 2<sup>nd</sup> order type has been designed in order to lock the reference frequency of the 16.36 MHz. Multiples analog and digital buffers have been added to achieve the integrated performance.

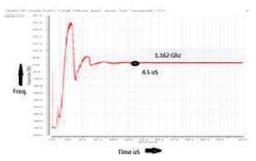

Fig.6 PLL test results Frequency vs Time

PLL is Locking successfully with the Lock range of 18 MHz

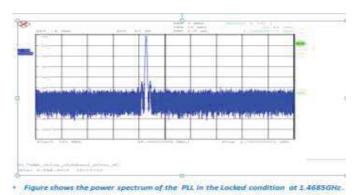

Fig. 7 Integrated PLL output power vs frequency

- Figure shows the Lock range of the PLL which is around 18 MHz.

- Successfully multiplication by 72 has been achieved.

Fig. 8 Lock range of the Integrated PLL

# LAYOUT:

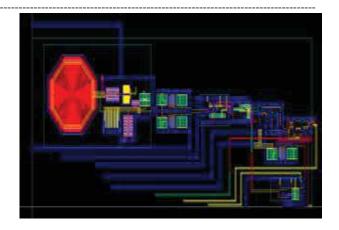

VCO integrated in the PLL have been fabricated in the 180 nm BiCMOS Towerjazz process. PLL is integrated with the Rx chain in the same chip.

Fig. 9 Layout of the Integrated PLL with the VCO

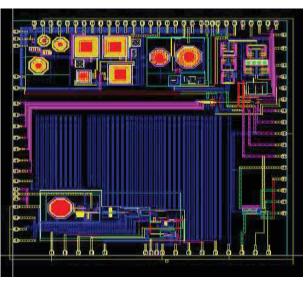

Fig. 10 Layout of the Integrated PLL in the integrated IRNSS -Rx chip

• Pin configuration of the Integrated Rx chip with PLL:

Fig.11 Integrated IRNSS- Rx Pin details

Fig.12 Fabricated dies in BiCMOS 180 nm Towerjazz process

#### 6. CONCLUSION:

Passive inductor based BiCMOS VCO can be used in various RF application with very good phase noise performance using HBT npn transistors. Using the HBT 180 nm SiGe BiCMOS process Low phase noise VCO has been designed and tested using very high Q inductors and performance is fully matched with the simulations.

#### **REFERENCES:**

[1] H. Jacobsson, "Very Low Phase-Noise Fully-integrated Coupled VCOs," IEEE RFIC symposium 2002

[2] P. Lai, S. Long, "A 5GHz pHEMT TransformerCoupled VCO," IEEE RFIC symposium 2005

[3] R.H. Talwekar and S.S. Limaye, "Design of High Performance Phase Locked Loop for UHF Band in 180 nm CMOS Technology," *Department of Electronics and Telecommunication*, DIMAT, Raipur (CG), India and Department of Electronic

# BIO DATA OF AUTHORS

Pankaj S Bhavsar has obtained her B.E. (Electronics Engg.) from Rajiv Gandhi Proudyogiki Vishwavidyalaya, Bhopal and M.E. (Digital Communication) from Devi Ahilya Vishwa Vidyalaya, Indore. She joined ISRO, Space Applications Centre, in 2006 and since then has been working in design and development of microwave circuits for Remote Sensing Satellites. She is pursuing

her Ph.D. from IIT Bombay,India on CMOS based RF and digital subsystems. Her research interests are in the design and development of the RF and digital mixed signaling ASIC's .She can be reached : pankajjain@sac.isro.gov.in and 114077001@iitb.ac.in

Dr. Jolly Dhar (IEEE-SM'09 and Scientist "G") received B.Tech., M.Tech.and Ph.D. in Radiophysics & Electronics from University of Calcutta in 1989, 1992 and 2013. She has designed and developed various pulsed SSPAs, CW SSPAs, presently she is working as Head MSRD for Frequency Generator, Receiver, Transreceive Modules, MMICs, Core-chips required for different Microwave remote sensing projects like RISAT-1, RISAT-2, L-SAR, Chandrayan mission II, Scatterometer and NISAR.

Ch V Narasimha Rao received Bachelor's degree in Electronics & Communications engineering from S V University, Tirupathi, India in 1989. Presently, he is leading the Microwave Sensors Transreceiver Group at SAC (ISRO) developing the high power transmit chain RF subsystems as well low power receiving chain RF subsystems for various microwave sensing payloads. He is

also a research scholar at DA-IICT, Gandhinagar.

Prof. Shalabh Gupta has obtained B.Tech in EE, from IIT Kanpur, MS and PhD: from EE, University of California Los Angeles, 2006-2009, He is the Asst. Prof. at IIT Bombay.He has 5 and more than 20 publications on CMOS and optical electronics.He can be availavile at <a href="http://www.ee.iitb.ac.in/~shalabh">http://www.ee.iitb.ac.in/~shalabh</a>

He is responsible for system design, planning and development of all Microwave Remote Sensing Payloads of ISRO. He has 2 granted patents, 6 pending patents,5 copyrights and more than 25 papers to his credit. He is the Ex. SAC director and working presently as a Senior Advisor ISRO, Head Quarter. He was the Project Director of RISAT project (Radar Imaging Satellite) of ISRO.During the course of RISAT realisation, he brought the

concept of core radar electronics which can be suited to a radar payload with mostly software modifications. In fact, all the payloads of DMSAR, RISAT and Scatterometer share same electronics with different versions of software. He can be reached at:misratapan@sac.isro.gov.in